Biography

Aurelio Morales Villanueva is a professor of the Electronics Engineering Department, College of Electrical and Electronics Engineering, at Universidad Nacional de Ingeniería (UNI), Perú. He has experience in presale, after sale and administration of data communication infrastructure projects and computing platforms in transnational companies in the telecommunications sector. His research interests include partial dynamic reconfiguration on FPGAs, computer architecture and embedded SoC on FPGAs, and digital ASIC VLSI design using open-source software tools.

- Dynamic Reconfiguration on FPGAs

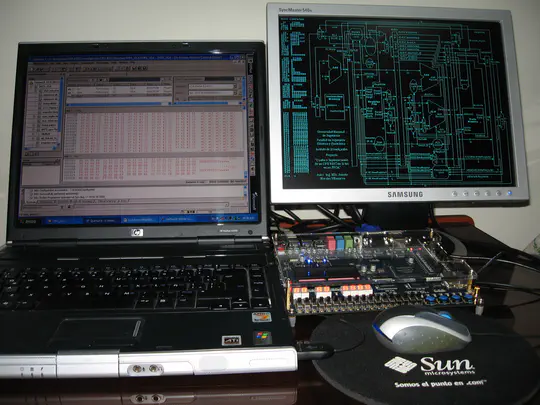

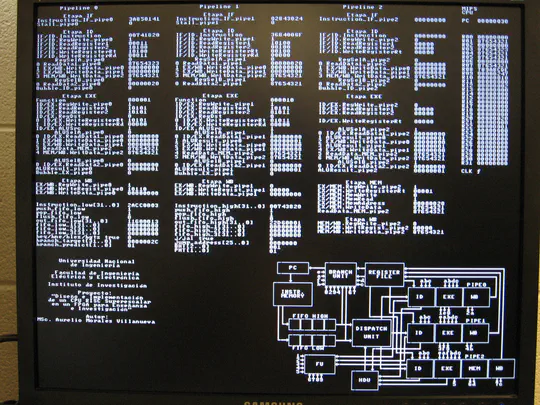

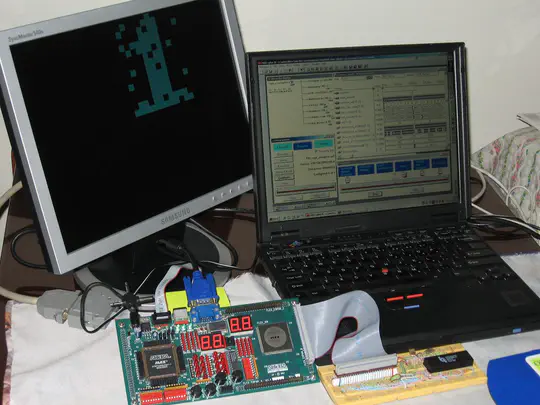

- Parallel/Distributed Computer Architecture

- FPGA-based System on Chip (SoC)

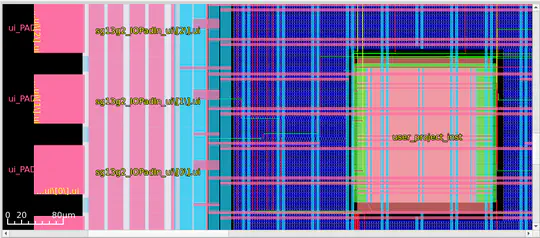

- Digital ASIC VLSI design using open-software tools

PhD in Electrical & Computer Engineering, 2015

University of Florida, U.S.A.

MSc in Electrical Engineering, 1994

State University of New York, Buffalo, U.S.A.

MSc in Electronics Engineering, 1991

Universidad Nacional de Ingeniería, Perú

BSc in Electronics Engineering, 1985

Universidad Nacional de Ingeniería, Perú

Skills

Professional Experience

Academic Experience

Projects

Journal & Conference Papers

Works that reference my research

Contact

- amorales@uni.edu.pe

- +51 381 6700

- Av. Túpac Amaru 210, Rimac, Lima 15333

- Friday 10:00 to 13:00